Cognome e Nome n. matr. Firma

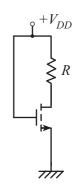

1) Nel circuito di figura il transistor NMOS ha il parametro  $k_n$  pari a 25  $\mu A/V^2$  e la tensione di soglia pari a 750 mV. La resistenza R vale 150  $k\Omega$  e la tensione di alimentazione  $V_{DD}$  è di 3.3 V. Si stabilisca il rapporto W/L del transistor affinché si abbia una tensione  $V_{DS}$  di 250 mV.

max.10/30

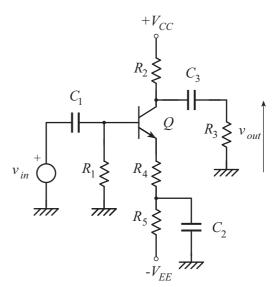

2) Nel circuito di figura le alimentazioni  $+V_{CC}$  e  $-V_{EE}$  sono pari, rispettivamente, a +12 V e -12 V; le resistenza  $R_1$ ,  $R_2$ ,  $R_3$ ,  $R_4$ e  $R_5$  valgono, rispettivamente,  $2 k\Omega$ ,  $300 \Omega$  e  $3.3 k\Omega$  $6 k\Omega$  $5.3 k\Omega$ condensatori  $C_1$ ,  $C_2$  e  $C_3$  valgono, rispettivamente, 200  $\mu F$ , 27  $\mu F$  e 100  $\mu F$ . Il transistor, al silicio, ha un  $\beta$  pari a 100. stabilito il aver punto funzionamento del transistor si valuti il guadagno  $v_{out}/v_{in}$  a centro banda e la frequenza di taglio determinata dai tre condensatori, (si assuma che  $V_T$  sia pari a 26 mV).

max.20/30