# Università degli studi di Lecce

Facoltà di Ingegneria Informatica Corso Nettuno

Progetto di un potenziometro digitale

**Studente: Tridici Daniele**

# Progetto di un potenziometro digitale

# Descrizione generale di un potenziometro

Per descrivere le funzioni di un potenziometro digitale è bene partire dal descrivere quelle di un potenziometro analogico.

Nella maggioranza dei circuiti è necessario effettuare un certo numero di regolazioni interne, che dipendono dalle loro modalità di funzionamento, oppure può essere necessario eseguire determinate correzioni in funzione dei gusti dell'utente. Queste operazioni sono rese possibili dall'impiego di resistenze, il cui valore può essere variato azionando dei comandi esterni.

I termini resistenza regolabile e potenziometro si trovano a essere sinonimi e, nella pratica, designano i medesimi componenti.

Il potenziometro consiste in una resistenza fissa collegata a due terminali di contatto, su cui si sposta un contatto mobile, collegato a un terzo terminale e azionato da un comando esterno, che può percorrerla da un estremo all'altro.

In questo modo, si può ottenere una resistenza del valore desiderato tra uno degli estremi del potenziometro e il contatto mobile. Vi è poi la possibilità di ottenere una determinata tensione al terminale corrispondente al contatto mobile, quando tra le due estremità viene applicata una differenza di potenziale.

Di seguito sono riportate alcune immagini relative a potenziometri analogici reali

potenziometri per regolazioni da circuito stampato

simbolo circuitale

potenziometro per regolazioni da pannello

I potenziometri vengono largamente utilizzati per applicazioni audio, video e strumentazione, ad esempio per controllare il volume di uno stereo, oppure posizionare i cursori di un oscilloscopio. Potrebbe essere comodo e preciso, effettuare le molteplici regolazioni che la tecnologia offre, utilizzando dei pulsanti, anziché una manopola. Ciò si ottiene utilizzando dei potenziometri digitali allo stato solido, dove il cursore, chiamato anche wiper, viene pilotato attraverso dei segnali digitali, i quali sono funzione degli step che si danno attraverso i pulsanti up e down. L'obbiettivo del progetto è appunto realizzare un potenziometro digitale, da utilizzare per applicazioni audio, utilizzando i circuiti integrati analizzati durante i corsi di elettronica I e II.

# Specifiche di progetto

Il potenziometro digitale deve avere le seguenti caratteristiche:

- una resistenza fissa pari a  $10 \text{ K}\Omega$ ;

- 16 posizioni possibili per il cursore;

- poter passare dalla posizione 0 alla 15 in 3 secondi;

- banda audio passante.

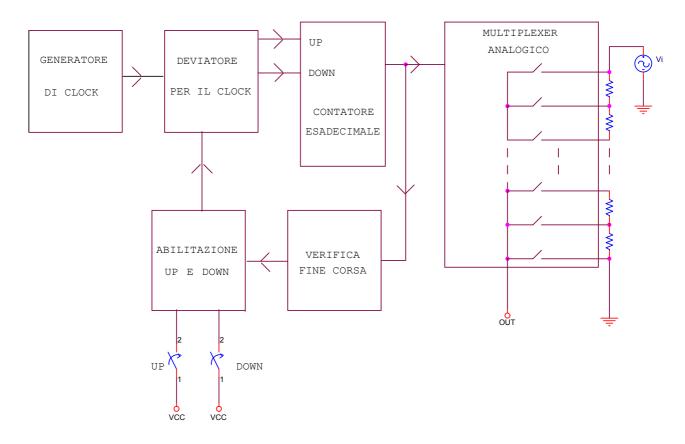

# Schema a blocchi del progetto

### Descrizione schema a blocchi

Nello schema si parte da un generatore di impulsi o clock. Il segnale generato viene inviato ad un deviatore, che ha la funzione di deviarlo su due linee separate, in funzione dei comandi Up e Down. Le uscite di quest'ultimo sono collegate ad un contatore esadecimale che conta gli impulsi di clock a seconda della durata degli impulsi Up o Down. Il contatore invia il suo stato a un multiplexer analogico che in funzione degli ingressi, chiude uno ed uno solo dei 16 interruttori al suo interno. Tra un interruttore e l'altro del multiplexer vi è una resistenza per un totale di un vettore di 15 resistenze di uguale valore.

Osservando lo schema, applicando tra un estremo e l'altro del vettore, una differenza di potenziale fissa o variabile, si ottiene un partitore di tensione e a seconda di quale interruttore viene chiuso, in uscita si ottiene una tensione compresa tra Vi e massa.

Lo stato del conteggio viene anche inviato ad un blocco di controllo che verifica la posizione di fine corsa del cursore: se questo si trova nella posizione 15, inviando altri impulsi Up, il contatore deve essere interdetto e mantenere il cursore in questa posizione; analogamente se si trova nella posizione 0, inviando altri impulsi Down il cursore deve rimanere in questa posizione. I segnali di verifica e di comando vengono inviati ad un blocco logico, che abilita l'incremento o il decremento del contatore, rispettivamente se il cursore non si trova nella posizione 15 oppure se il cursore non si trova nella posizione zero.

Per generare gli impulsi al fine di incrementare o decrementare il contatore, basterebbero i soli impulsi di comando Up e Down, mentre la scelta di aggiungere un generatore di impulsi, deriva dal fatto che l'utilizzatore potrebbe essere interessato a spostare il cursore tra due posizioni lontane, mantenendo premuto il pulsante di comando, invece di premerlo tante volte quanto dista la nuova posizione.

# Analisi dei singoli blocchi e loro progettazione

### Generatore di clock

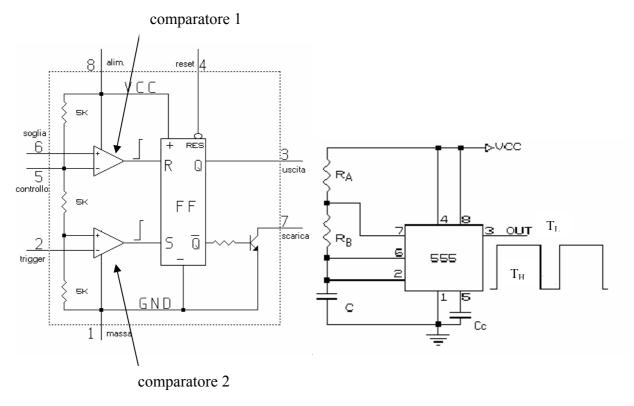

#### Breve analisi teorica del timer 555

Per realizzare il generatore di clock si è utilizzato il timer integrato 555 in configurazione astabile. Di seguito è riportato lo schema a blocchi e la configurazione astabile del timer:

I componenti base del dispositivo sono: due comparatori di soglia , un latch S/R, e un transistor bipolare configurato come interruttore in parallelo con la serie C - RB nel caso della

configurazione astabile. Le tre resistenze identiche stabiliscono le tensioni di riferimento Vs1 e Vs2 rispettivamente dei comparatori 1 e 2; si ha Vs1 = Vcc2/3 e Vs2 = Vcc/3.

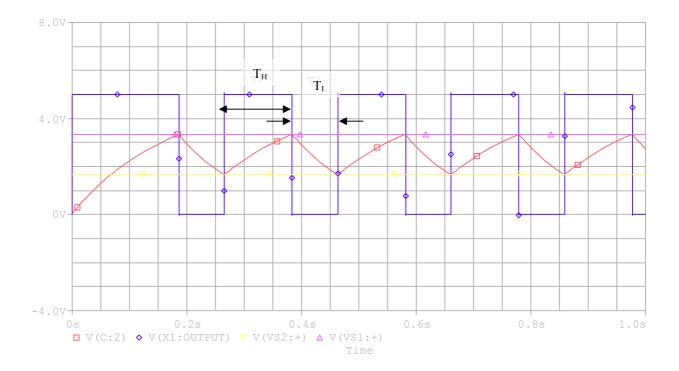

Per capire il funzionamento di questo dispositivo si analizza il seguente grafico ricavato con il simulatore:

il segnale viola, rappresenta l'uscita, quello rosso, la carica e scarica del condensatore C e le due rette rappresentano le soglie dei due comparatori.

Si supponga che il condensatore sia inizialmente scarico e che il latch abbia l'uscita Q a livello alto, in questa situazione il transistor è in interdizione e il condensatore si carica verso Vcc attraverso le resistenze RA e RB; appena la tensione sul condensatore tocca la soglia Vs1, l'uscita del comparatore 1 commuta a livello alto e di conseguenza l'uscita Q del latch commuta a livello basso. In questa nuova situazione il transistor è in saturazione e scarica C attraverso RB. Appena la tensione sul condensatore tocca la soglia Vs2, l'uscita del comparatore 2 commuta a livello alto e di conseguenza l'uscita Q del latch commuta a livello basso e il ciclo si ripete.

I semiperiodi T1 e T2 vengono calcolati utilizzando le seguenti relazioni fornite dal costruttore:

$$T_H = (RA + RB)*C*ln2$$

e  $T_L = RB*C*ln2$ .

Per interrompere il ciclo del generatore, si deve portare il pin RESET (pin n°4) ad un livello basso, ovvero fin quando il suo potenziale è a livello alto il ciclo è abilitato. Interrompendo il ciclo l'uscita si porta ad un livello prossimo a massa. Osservando la figura relativa alla configurazione astabile del generatore, il pin RESET è collegato alla tensione di alimentazione, in modo tale da ottenere un clock fisso da deviare in funzione dei comandi Up e Down.

Per settare le tensioni di riferimento Vs1 e Vs2, si deve stabilire una polarizzazione Vt per l'ingresso CONTROL (n° 5): in questo modo i livelli tra cui si scarica o si carica il condensatore saranno Vt/2 e Vt anziché Vcc/3 e 2Vcc/3. Al contrario, qualora ci si accontenti dei livelli 2Vcc/3 e Vcc/3, il pin 5 può essere, in principio, lasciato aperto. Tuttavia, in tale circostanza può essere captato del rumore di questo pin lasciato aperto e questo livello aggiuntivo modifica il livello preesistente. Siccome la durata dei cicli di scarica e carica del condensatore dipende da tale livello, si otterrebbe una variazione dei tempi. Mettendo a massa il pin con un condensatore, si annullano i disturbi di alta frequenza che troverebbero un percorso di ritorno a massa a più bassa impedenza attraverso il condensatore, inoltre si accresce l'immunità del dispositivo alle variazioni istantanee della tensione di alimentazione, che sarebbero compensate dalla carica immagazzinata nel condensatore. Il valore del condensatore consigliato dal costruttore è 1nF.

### Configurazione del timer per il progetto

Nelle specifiche di progetto, si richiede che il potenziometro debba poter passare dalla posizione zero alla 15 in 3 secondi, quindi il timer 555 deve essere configurato in modo tale da generare 15 periodi nel medesimo intervallo, ovvero il periodo T del clock è pari a 200ms.

Per quanto riguarda il duty cycle non si è interessati a un DC = 50%, in quanto per motivi relativi alla tecnologia del contatore, è il solo fronte di salita che fa commutare il contatore oppure il fronte di discesa, nel caso il segnale venga ulteriormente negato; quindi per essere in accordo con le specifiche di progetto, basta avere un onda rettangolare che abbia una frequenza del fronte di salita pari a 5 Hz.

Per calcolare il valore delle 2 resistenze si sceglie  $T_L = 80 \text{ms}$ ,  $T_H = 120 \text{ms}$ .

Fissando  $C = 24\mu F$ , si ha:

$$RB = \frac{T_L}{C * \ln 2} = \frac{80ms}{24\mu F * \ln 2} = 4808\Omega, \text{ con valore standard pari a 4.7 K}\Omega;$$

$$RA = \frac{T_H}{C * \ln 2} - R2 = \frac{120ms}{24\mu F * \ln 2} - 4808\Omega = 2405\Omega, \text{ con valore standard pari a 2.4 K}\Omega.$$

Utilizzando i valori standard, la durata dei semi periodi è data da:

$T_L = 4.7~K\Omega * 24~\mu F * ln2 = 78~ms$  e  $T_H = (4.7~K\Omega + 2.4~K\Omega) * 24~\mu F * ln2 = 118~ms$ , da cui si ricava il periodo T = 196ms e la frequenza f = 5.1~Hz, molto prossima alle specifiche di progetto. Per quanto riguarda la simulazione, il grafico visto per il funzionamento del timer, fa proprio riferimento alla configurazione per il progetto.

#### Contatore esadecimale

#### Breve analisi teorica sui contatori

Nei circuiti digitali i contatori sono utilizzati per contare gli impulsi applicati al suo ingresso, dando in uscita lo stato del conteggio in forma binaria. I contatori sono dei circuiti sequenziali realizzati con le diverse tipologie di flip-flop: JK, D e T .

I contatori si classificano in due categorie:

- asincroni: il clock viene applicato al flip-flop corrispondente al bit meno significativo, e si propaga in modo seriale verso il bit più significativo;

- sincroni: il clock arriva contemporaneamente a tutti i flip-flop.

Per entrambe le categorie i contatori possono essere:

- up-down: il conteggio può essere effettuato sia nella direzione normale che in quella inversa.

- decimali: il conteggio va da 0 a 9;

- esadecimali: il conteggio va da 0 a 15;

- presettabili: il conteggio parte da un certo numero in poi.

Alcuni contatori hanno in uscita il pin di riporto per la modalità up, e il pin di prestito per la modalità down, da collegare come clock ad un altro contatore in cascata. Ad esempio N contatori decimali possono essere collegati in cascata per ottenere un conteggio a N cifre decimali.

### Contatore utilizzato per il progetto

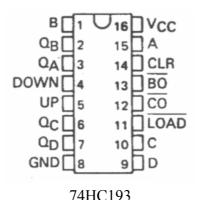

L'integrato 74HC193 è un circuito realizzato con tecnologia CMOS, contenente un contatore con le seguenti caratteristiche: realizzato con flip-flop di tipo T, sincrono, esadecimale, up-down e presettabile.

Di seguito viene riportata la descrizione dei pin:

Vcc, GND: ingressi per l'alimentazione;

A,B,C,D: ingressi per il preset;

Qa,Qb,Qc,Qd: uscita binaria dello stato del conteggio; UP: ingresso del clock per il conteggio normale; DOWN: ingresso del clock per il conteggio inverso;

CLR: ingresso per l'azzeramento;

LOAD^: ingresso per l'abilitazione del preset;

BO^: uscita per il prestito; CO^: uscita per il riporto.

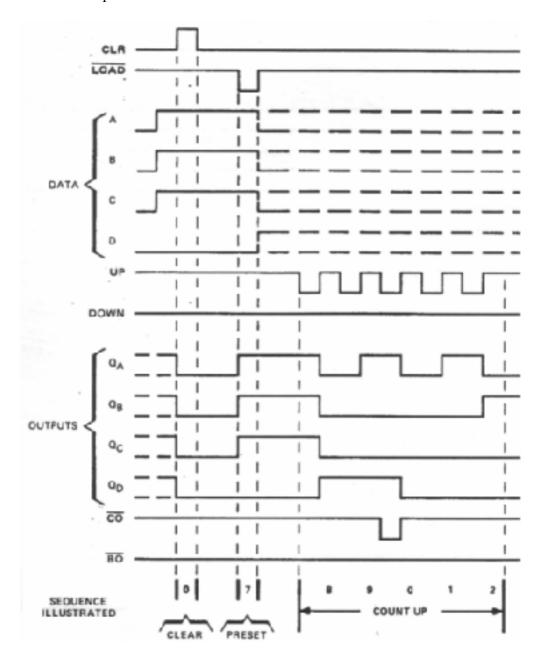

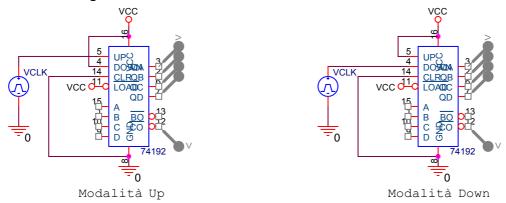

Per la modalità up, il clock viene applicato in UP, mantenendo a livello alto il pin DOWN. Per la modalità down, il clock viene applicato in DOWN, mantenendo a livello alto il pin UP. Il funzionamento del dispositivo viene illustrato sul data scheet con un diagramma temporale; in particolare una prima illustrazione è relativa al preset del numero sette e al conteggio da questo in poi, nella modalità up :

è possibile notare che il contatore viene prima azzerato sul fronte di salita del segnale di CLEAR e poi settato sul fronte di discesa del segnale di  $LOAD^{\wedge}$ , inoltre, le uscite commutano sul fronte di salita del clock.

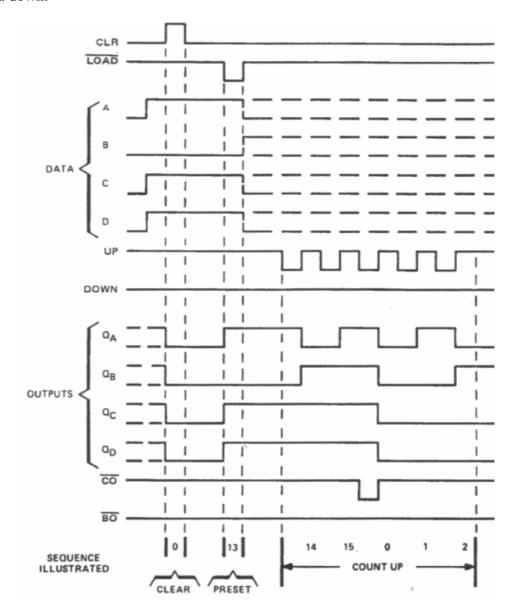

Una seconda illustrazione è relativa al preset del numero 13 e al conteggio da questo in poi nella modalità down:

Come e stato già visto nell' esperienza di laboratorio , nella pratica il contatore può essere configurato come segue:

Per la simulazione con PSPICE, basta portare il pin LOAD a livello alto (VCC) e settare a 0 lo stato iniziale dei flip-flop, attraverso Simulation Setting.

Sia per la simulazione che per il caso pratico il conteggio inizia da zero.

### **Deviatore per il clock**

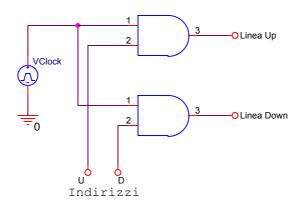

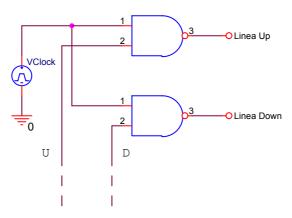

Per costruire un deviatore adatto per il progetto, si può partire dal seguente circuito combinatorio realizzato con due porte AND (mod. 74HC08):

Il segnale di clock è collegato in parallelo ad entrambe le porte e per deviarlo in una delle 2 linee, lasciando a livello basso l'altra, basta portare ad 1 (livello logico alto) una delle linee indirizzo; per esempio per deviarlo sulla linea Up, basta portare a 1 l'indirizzo U e a 0 (livello logico basso) l'indirizzo D.

Nel caso in cui entrambi gli indirizzi siano ad 1, per evitare di portare il segnale ad entrambe le linee, bisogna aggiungere un blocco logico prima di applicare i pulsanti di comando.

Il blocco logico può essere costruito utilizzando la seguente tabella di verità:

| Ing | ressi | Uscite |   |

|-----|-------|--------|---|

| Up  | Down  | U      | D |

| 0   | 0     | 0      | 0 |

| 0   | 1     | 0      | 1 |

| 1   | 0     | 1      | 0 |

| 1   | 0     | 0      | 0 |

dalla quale si ricava  $U = AND(Up, Down^{\wedge}) e D = AND(Up^{\wedge}, Down)$

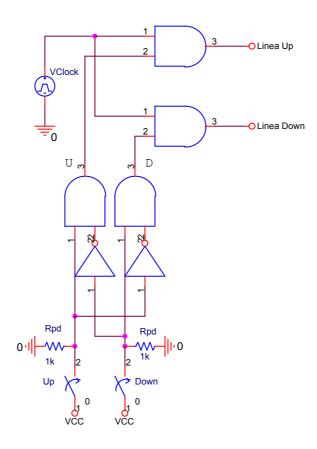

Il deviatore completo è dato dal seguente circuito:

Per realizzare le funzioni ricavate dalla tabella di verità si sono aggiunte due porte AND e due NOT (mod. 74HC04). Le due resistenze di pull down, servono a mantenere a livello basso gli ingressi quando i pulsanti sono aperti.

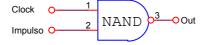

Un'altra osservazione deriva dall'analisi del 74HC193 dove risulta che per la modalità up, bisogna collegare il clock al pin UP e mantenere a livello alto il pin DOWN; viceversa per la modalità down bisogna collegare il clock al pin DOWN e mantenere a livello alto il pin UP. Il deviatore analizzato devia sì il clock su una delle due linee, ma lasciando l'altra a livello basso. Una soluzione per questo problema è sostituire le due porte AND con due NAND (mod. 74HC00):

in questo modo si ottiene sempre un deviatore, con la differenza che la linea non scelta rimane a livello alto e le uscite del contatore commutano sul fronte di discesa del clock.

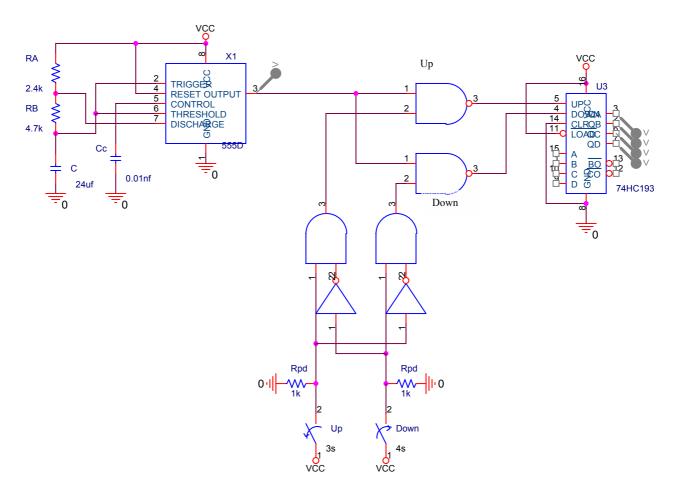

# Unione dei blocchi analizzati e simulazione

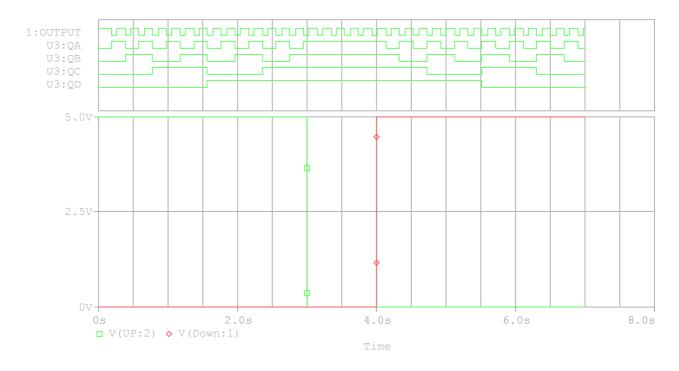

I due interruttori sono configurati per simulare la premuta, per 3 secondi, del pulsante Up e dopo 1s, la premuta del pulsante Down.

### Di seguito è riportato il risultato della simulazione:

#### Problema del clock fisso

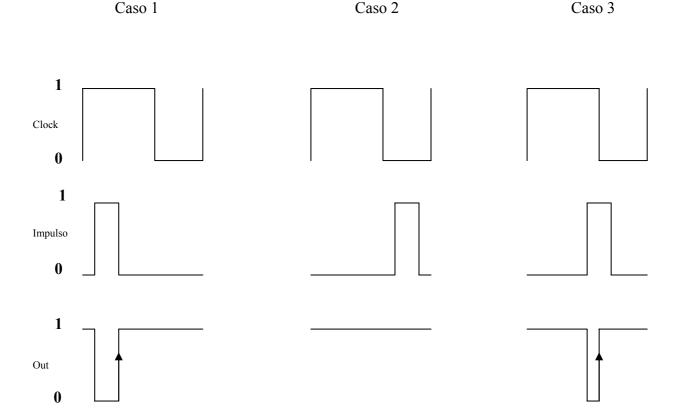

La precedente simulazione non rende visibile un problema legato alla scelta di un clock fisso da deviare in funzione dei comandi esterni.

Per capire il problema si consideri il seguente esempio: per incrementare di un'unità il contatore, si manda in ingresso nella porta NAND-Up, il clock e un impulso di durata t dovuto alla premuta del pulsante Up; supponiamo che la durata t minima dell'impulso sia di 60ms. Mandando contemporaneamente in ingresso il clock e l'impulso, si possono avere 3 casi distinti:

| Clock | Impulso | Out |

|-------|---------|-----|

| 0     | 0       | 1   |

| 0     | 1       | 1   |

| 1     | 0       | 1   |

| 1     | 1       | 0   |

Osservando l'uscita, nei casi 1 e 3, il contatore sarà incrementato, poiché in parte o completamente l'impulso coincide con il livello alto del clock, nel caso 2 invece l'impulso coincide completamente con il livello basso e di conseguenza non ci sarà nessun incremento.

#### Soluzione del problema

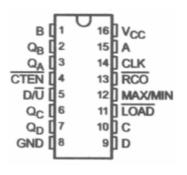

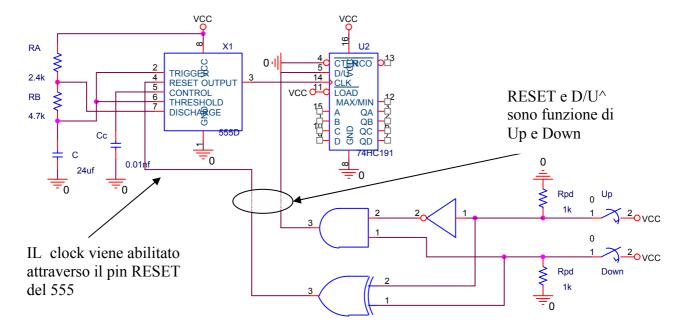

Il problema si risolve scegliendo di configurare il circuito, con un clock che viene abilitato dai comandi esterni Up e Down. Questa funzione è resa possibile con il pin RESET del timer 555. Un' altra modifica è relativa al contatore, ovvero si sostituisce il 74HC193 con il 74HC191. Sostanzialmente questo contatore ha le stesse funzioni del 193, il vantaggio è la presenza di un pin per il clock e di un pin U^/D, con il quale si seleziona la modalità di conteggio:

Di seguito viene riportata la descrizione dei pin:

Vcc, GND: ingressi per l'alimentazione;

A,B,C,D: ingressi per il preset;

Qa,Qb,Qc,Qd: uscita binaria dello stato del conteggio; D/U^: ingresso per la modalità di conteggio;

CLK: ingresso per il clock;

CTEN^: ingresso per l'abilitazione del conteggio; LOAD^: ingresso per l'abilitazione del preset;

MAX/MIN: uscita per lo stato di overflow e underflow del contatore; RCO^: uscita per il riporto o prestito in funzione dell'ingresso D/U^

Le funzioni del contatore sono intuibili attraverso la seguente tabella di verità:

| INPUTS |      |     |     | ELINCTION           |  |

|--------|------|-----|-----|---------------------|--|

| LOAD   | CTEN | D/Ū | CLK | FUNCTION            |  |

| н      | L    | L   | 7   | Count up            |  |

| н      | L    | н   | 7   | Count down          |  |

| L      | х    | х   | х   | Asynchronous preset |  |

| н      | н    | Х   | Х   | No change           |  |

per la modalità up, il pin  $D/U^{\wedge}$  deve esse portato a livello basso, mentre per la modalità down bisogna portarlo a livello alto.

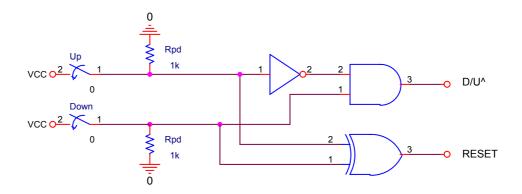

Per interfacciare i segnali di comando con il generatore di clock e il contatore, è necessario costruire un nuovo blocco logico che attivi o disattivi i pin RESET e D/U^, in funzione di Up e Down come riportato nella seguente tabella di verità:

| Ing | ressi | Us    | cite |

|-----|-------|-------|------|

| Up  | Down  | RESET | D/U^ |

| 0   | 0     | 0     | 0    |

| 0   | 1     | 1     | 1    |

| 1   | 0     | 1     | 0    |

| 1   | 1     | 0     | 0    |

dalla quale si ricava RESET = EXOR(Up, Down) e  $D/U^{\wedge}$  = AND(Up $^{\wedge}$ ,Down)

# Unione dei blocchi analizzati e simulazione

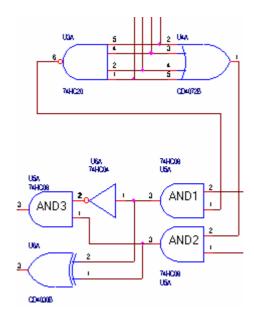

Per la porta EXOR si è scelto l'integrato mod. CD4030A.

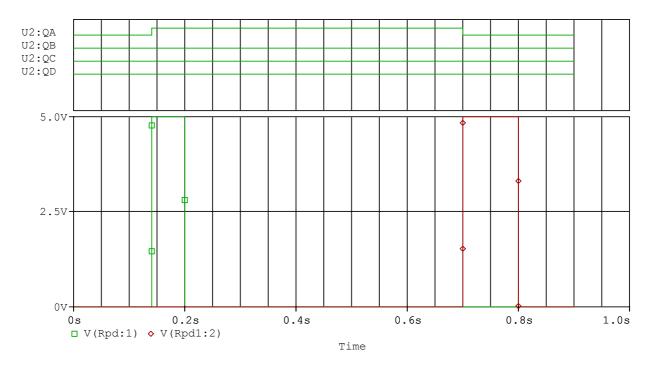

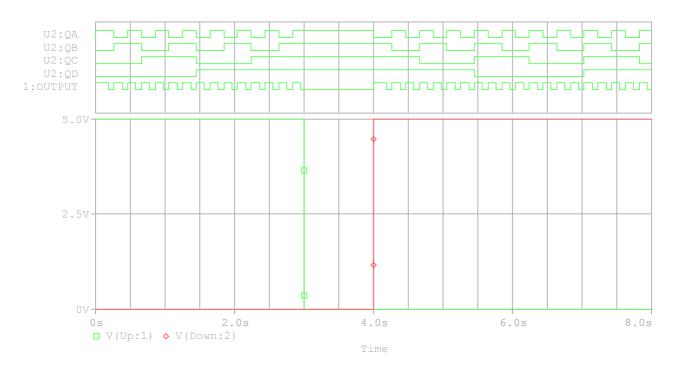

Una prima simulazione fa riferimento alla premuta del pulsante Up per 60ms e dopo 0.5s, la premuta del pulsante Down per 100ms:

Osservando il diagramma temporale, il contatore viene incrementato di una unità sul fronte di salita dell'impulso "Up", in verde. Successivamente il contatore viene decrementato di una unità, sul fronte di salita dell'impulso "Down", in rosso.

Una seconda simulazione fa riferimento alla premuta del pulsante Up per 3s e dopo 1s, la premuta del pulsante Down :

Osservando il diagramma temporale, quando entrambe i pulsanti sono aperti, il clock è disabilitato.

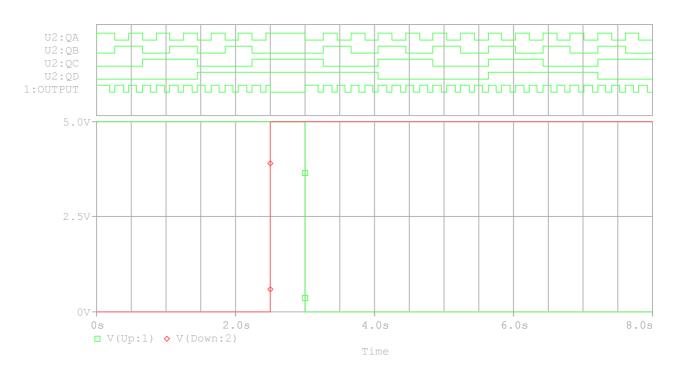

Una terza simulazione fa riferimento alla premuta contemporanea di entrambe i pulsanti:

Durante l'intervallo compreso tra 2.5s e 3s, entrambi i pulsanti sono chiusi e come è possibile osservare il clock viene disabilitato.

# **Multiplexer Analogico**

### Breve analisi teorica del multiplexer analogico

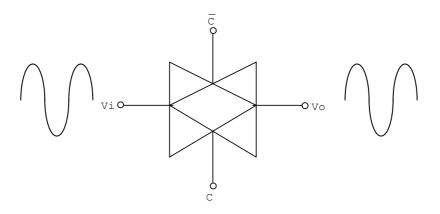

Un multiplexer seleziona una tra N sorgenti e ne trasmette il segnale analogico su una singola linea. Il componente fondamentale di questo dispositivo è la porta di trasmissione CMOS, ovvero un interruttore analogico che viene pilotato dal pin C:

I parametri fondamentali per questo componente sono:  $\mathbf{r}_{on}$ , la resistenza vista tra Vi e Vo quando la porta trasmette il segnale, il tempo di commutazione e la banda passante.

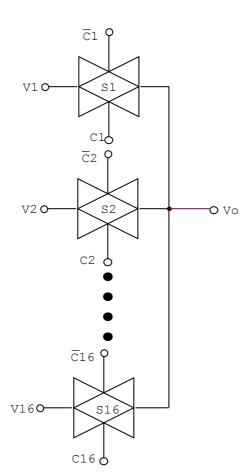

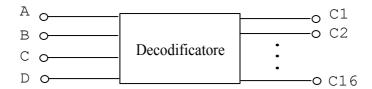

Nella seguente figura è descritto lo schema a blocchi di un multiplexer analogico con 16 ingressi:

Se Ck è uguale a 1, la porta CMOS trasmette il segnale analogico  $v_k$  all'uscita, mentre se Ck è 0, la trasmissione è inibita.

Lo schema a blocchi precedente viene completato aggiungendo un decodificatore con 4 linee di ingresso e 16 linee di uscita:

In generale un decodificatore è un circuito combinatorio con n linee di ingresso (nel caso del progetto sono provenienti dal contatore) e 2<sup>n</sup> linee di uscita; di queste è attiva (livello logico alto) solo quella corrispondente al valore applicato in ingresso: ad esempio per il 4-16, se l'ingresso è 1111 (ABCD), l'uscita attiva sarà C16.

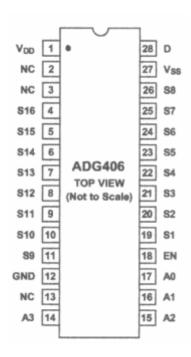

### Multiplexer utilizzato per il progetto

L'integrato ADG406 è un circuito realizzato con tecnologia CMOS, contenente un multiplexer analogico con le seguenti caratteristiche:

- $-t_{on} < 160 \text{ns}, t_{on} < 150 \text{ns};$

- $r_{on}$  = 80  $\Omega$  (valore massimo);

- utilizzabile anche per applicazioni audio.

Di seguito viene riportata la descrizione dei pin:

VDD, VSS, GND: ingressi per l'alimentazione;

S1-S16: linee di ingresso;

A1- A3: ingressi per la selezione della linea  $S_k$ ;

EN: abilitazione del multiplexer;

D: linea di uscita.

Il pin VSS viene utilizzato per l'alimentazione negativa, ma si può anche scegliere di collegarlo a massa, ottenendo caratteristiche diverse rispetto all'alimentazione duale.

#### Vettore di resistenze

Come già anticipato, per ottenere le diverse cadute di tensione da selezionare con il multiplexer, si utilizza un vettore di resistenze collegate in serie. Facendo riferimento alle specifiche di progetto, il vettore deve contenere 15 resistenze, con resistenza equivalente pari a 10 K $\Omega$ . Il valore di una singola resistenza è dato da  $10k\Omega/15 = 667 \Omega$  con valore standard  $680 \Omega$ .

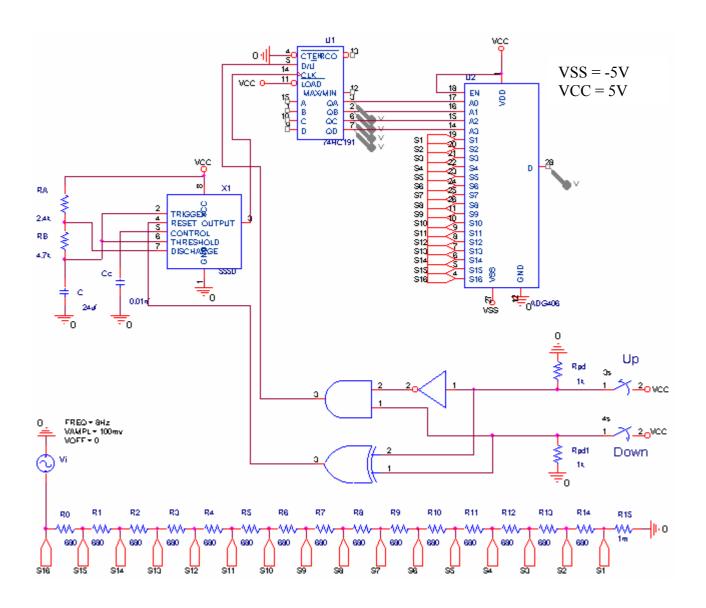

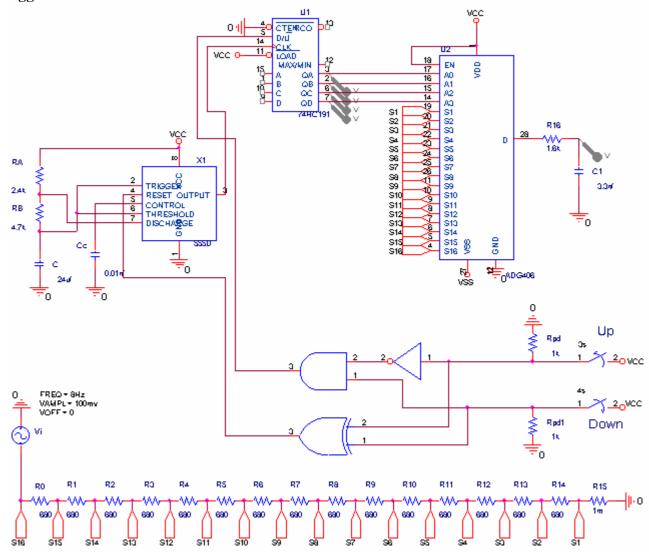

### Unione dei blocchi analizzati e simulazione

Per simulare il circuito si è aggiunta una resistenza (R 15) prossima a zero e per una grafica migliore, per collegare il multiplexer con il vettore di resistenze, si è preferito utilizzare i link. Il segnale analogico Vi , è un'onda sinusoidale con ampiezza 100mV e frequenza 8Hz e viene collegato alla linea 16 del multiplexer, ovvero la posizione selezionata dal contatore quando il suo stato è al massimo valore.

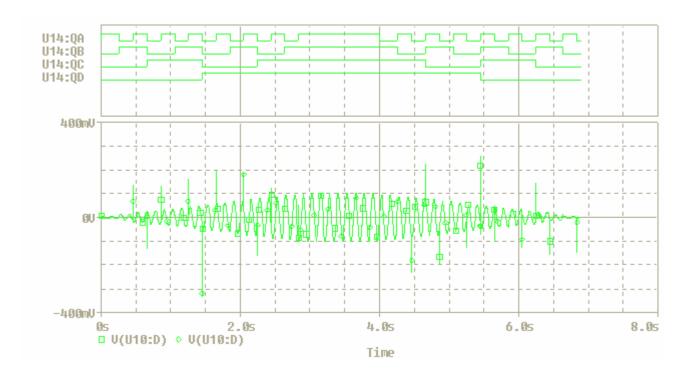

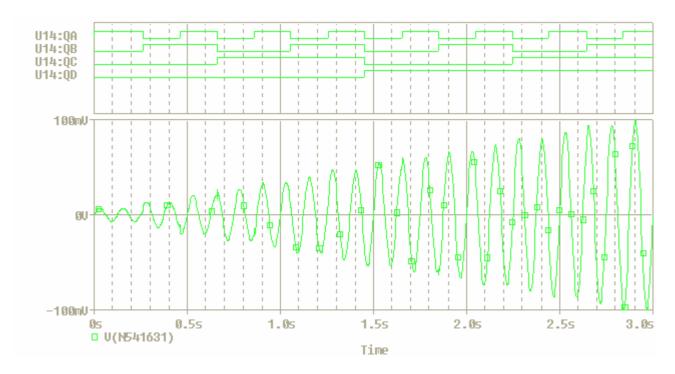

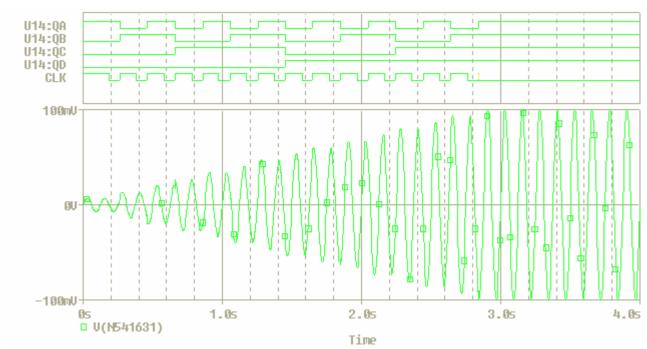

La seguente simulazione fa riferimento alla premuta del pulsante Up per 3s e dopo 1s, la premuta del pulsante Down:

Osservando il diagramma temporale, per i primi 3 secondi, ad ogni incremento del contatore, l'ampiezza del segnale in uscita dal multipexer aumenta, fino ad arrivare a 100mV; successivamente entrambe i pulsanti sono aperti e il segnale rimane con la massima ampiezza fino al quarto secondo, da qui in poi il contatore inizia a decrementarsi riducendo il segnale a zero.

### Progetto del filtro per lo stadio di uscita

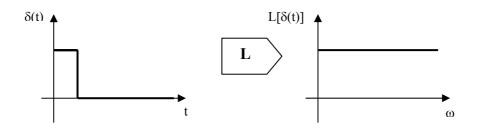

Osservando il diagramma precedente, in corrispondenza di ogni step, il segnale analogico presenta dei disturbi dovuti alla carica e scarica della capacità parassita dello stadio di uscita. Questi disturbi possono essere approssimati dalla funzione impulsiva o delta di Dirac. La trasformata di Laplace per questa funzione è 1 ovvero una frequenza di taglio superiore infinita:

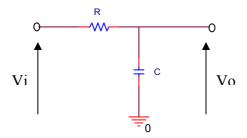

La frequenza di taglio superiore del multiplexer è circa 20 Mhz ed essendo interessati alla banda audio, può essere ridotta a 30 Khz applicando in uscita un filtro passa basso:

sapendo che deve essere soddisfatta la relazione  $\frac{1}{\sqrt{1+\omega^*R^*C}}=\frac{1}{\sqrt{2}}$ , dove  $\omega=2\pi f$ , fissando C=3.3nf e f=30 Khz , si ottiene R=1608  $\Omega$  con valore standard 1,6 K $\Omega$ .

### Aggiunta del filtro e simulazione

## Verifica di fine corsa e abilitazione Up e Down

Se lo stato del contatore è al valore massimo o minimo, il potenziometro digitale è giunto a fine corsa e con il circuito ottenuto, mandando un nuovo impulso si ricomincia a contare rispettivamente da **0000** o da **1111**. Per evitare questa situazione, è necessario bloccare il contatore quando il suo stato è giunto al valore massimo o minimo, ovvero se l'utilizzatore insiste nell'ulteriore incremento o decremento, dovrà essere vincolato a scegliere di lasciare il potenziometro a fine corsa oppure cambiare modalità. Per ottenere questa funzione si parte dalla logica che verifica gli stati estremi del contatore:

- per verificare lo **0000**, basta portare le uscite del contatore in una porta OR a 4 ingressi; l'uscita della porta sarà **0** solo se tutti gli ingressi sono a **0**;

- per verificare lo stato 1111, basta portare le uscite del contatore in una porta NAND; l'uscita della porta sarà 0 solo se tutti gli ingressi sono a 1.

Il risultato delle due verifiche può essere utilizzato per abilitare l'incremento o il decremento del contatore; ciò si ottiene utilizzando due porte AND: in una si porta la verifica dello stato 1111 e lo stato del pulsante Up, nell'altra la verifica dello stato 0000 e lo stato del pulsante Down. Le uscite delle due porte andranno nel blocco logico che genera il RESET del 555 e D/U^ del contatore. In questo modo il contatore sarà aggiornato in funzione degli stati estremi dello stesso.

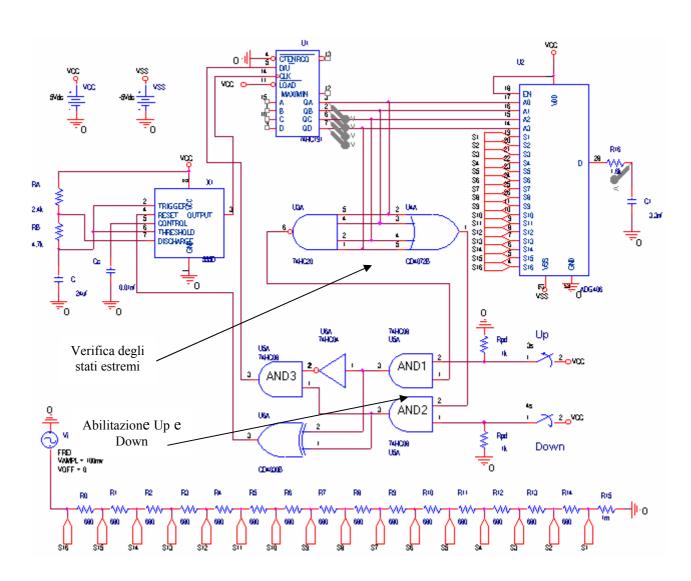

# Circuito completo e simulazione

### Elenco componenti

| Integrati |         |                       | Resist            | enze e capacità       |

|-----------|---------|-----------------------|-------------------|-----------------------|

| X1        | NE555   | generatore di clock   | RO – R15          | 680Ω                  |

| U1        | 74HC191 | contatore esadecimale | Rpd               | 1ΚΩ                   |

| U2        | ADG406  | mux analogico         | RA                | 2,4ΚΩ                 |

| U3        | 74HC20  | NAND 4 ingressi       | RB                | 4,7ΚΩ                 |

| U4        | CD4072B | OR 4 ingressi         | C (elettrolitico) | 24μF                  |

| U5        | 74HC08  | AND 2 ingressi        | Cc(poliestere)    | 1nF                   |

| U6        | CD4030B | EXOR                  | Up, Down pulsa    | nti normalmete aperti |

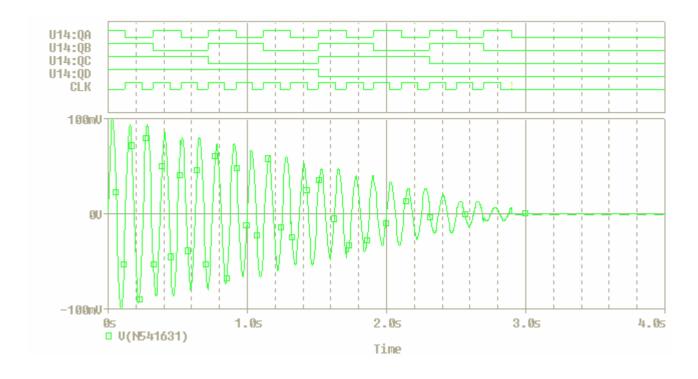

Con la seguente simulazione si è verificato il funzionamento delle due porte per la verifica degli stati estremi del contatore:

Osservando il diagramma temporale, il clock è abilitato fin quando il contatore non arriva allo stato 1111; da qui in poi anche se il pulsante Up è chiuso, il segnale analogico rimane alla massima ampiezza.

Osservando il diagramma temporale, il clock è abilitato fin quando il contatore non arriva allo stato **0000**; da qui in poi anche se il pulsante Down è chiuso, il segnale analogico rimane alla minima ampiezza.

Il funzionamento del circuito è stato già analizzato con la descrizione dello schema a blocchi. Dopo aver modificato lo schema di partenza si riassume il tutto analizzando lo schema elettrico del progetto completo:

- Il pulsante Up, normalmente aperto, è collegato a alla porta AND1 che abilita l'incremento del contatore se e solo se l'uscita della porta OR è a 1;

- Il pulsente Down, normalmente aperto è collegato alla porta AND2 che abilita il decremento del contatore se e solo se l'uscita della porta NAND e a 1;

- Entrambe i pulsanti sono dotati di una resistenza di pull-down per portare a zero l'ingresso della porta AND quando il pulsante è aperto;

- Le uscite delle due porte AND sono collegate a un blocco logico che genera il RESET del 555 e D/U^ del contatore, in funzione dei comandi esterni;

- Il timer 555 è configurato per generare un segnale di clock con una frequenza di 5 Hz. Il clock viene abilitato con il pin RESET: se l'impulso dovuto alla premuta di uno dei pulsanti ha una durata inferiore a 200ms, il contatore collegato all'uscita del timer, viene incrementato o decrementato di una sola unità; se è superiore a 200ms il timer genera un'onda rettangolare per la stessa durata dell'impulso, incrementando o decrementando il contatore di più unità;

- Lo stato del contatore viene inviato negli ingressi (A0-A3), di selezione del multiplexer. Le 16 linee sonno collegate alle diverse cadute di tensione del segnale Vi, ottenute con il vettore di resistenze collegate in serie;

- Infine il segnale d'uscita del multiplexer viene filtrato con un filtro passa basso, per eliminare i disturbi dovuti alla carica e scarica della capacità parassita dello stadio di uscita.

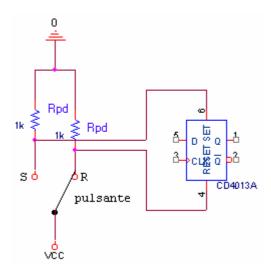

## Antirimbalzi per i pulsanti Up e Down

La maggior parte dei pulsanti meccanici rimbalza più volte prima di assestarsi nella posizione di chiusura. Per evitare di commutare più volte lo stato del contatore, può essere utilizzato un flip-flop per dare in uscita un unico cambiamento di stato, quando il pulsante si chiude per la prima volta, senza essere influenzato dai rimbalzi che eventualmente possono seguire. Si consideri il seguente circuito dove si utilizza un flip-flop di tipo D:

Il pulsante unipolare a due contatti è inizialmente nalla posizione R, in cui connette Reset a Vcc, ovvero Reset = Vcc e Q = 0. Se il pulsante viene premuto, il contatto passa dalla posizione R alla posizione S, in cui connette Set a Vcc, ovvero Set = Vcc e Q = 1. Grazie alle resistenze di pull-up, quando il contatto è connesso al vuoto, si ha Set = Reset = 0, ovvero lo stato di memoria del flip-flop, quindi se il contatto rimbalza prima di assestarsi, vuol dire che oscillerà tra S e il vuoto, ovvero S oscillerà tra Vcc e lo stato di memoria , lasciando inalterato Q .

#### Analisi di Montecarlo

L'analisi di Montecarlo del simulatore Pspice è usata per valutare il rendimento e le statistiche di performance di un disegno. Prima di lanciare il profilo di simulazione per ogni analisi di Montecarlo, ogni parametro dei componenti viene variato casualmente in base al range di tolleranza. Dopo ogni simulazione, le misure abilitate sono calcolate e il risultato memorizzato per l'analisi statistica.

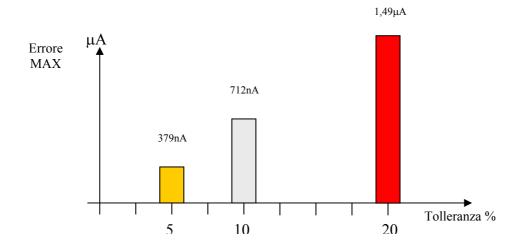

Questo tipo di analisi può essere utilizzata per misurare l'errore di non linearità integrale del potenziometro, al variare della tolleranza scelta per le resistenze del vettore, in particolare il valore massimo, quello minimo e il valore tipico (la media) per questa grandezza .

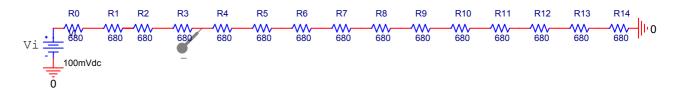

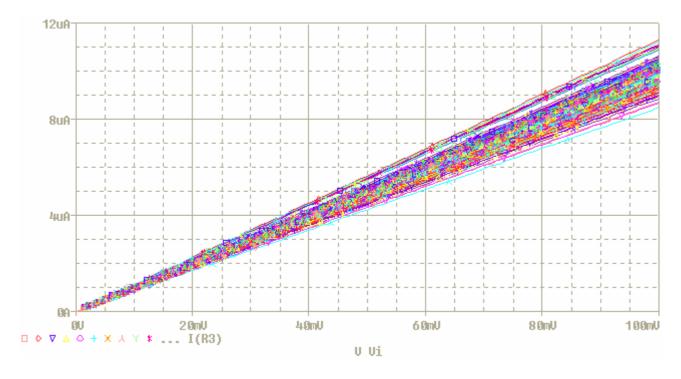

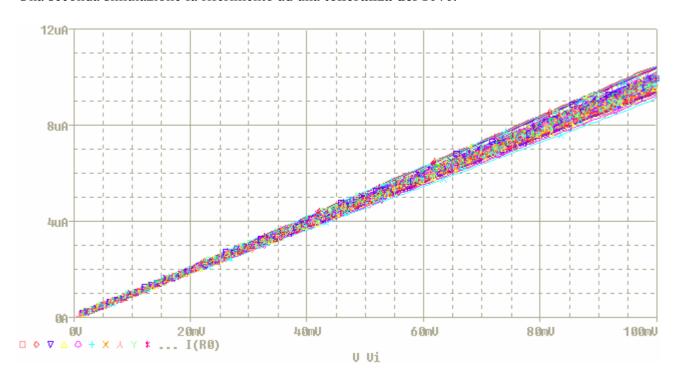

Per effettuare tale misura basta analizzare il solo vettore di resistenze:

Si imposta un'analisi DC Sweep al fine di ottenere una retta che rappresenta la variazione della corrente I, che attraversa il vettore, al variare di Vi (da 0 a 100mV). Insieme a questa analisi si imposta l'analisi di Montecarlo al fine di ottenere un fascio di rette con ampiezza diversa a seconda della tolleranza che si sceglie per le resistenze.

Una prima simulazione fa riferimento ad una tolleranza del 20%

In corrispondenza di Vi = 100 mV si ha:

- corrente massima = 11,294 μA;

- corrente minima =  $8,47 \mu A$ ;

- corrente nominale =  $9,804 \mu A$ ;

L'errore di non linearità integrale è dato da:

- (corrente nominale corrente minima) =  $1,334 \mu A$  (valore minimo);

- (corrente massima corrente nominale) =  $1,49 \mu A$  (valore massimo);

Una seconda simulazione fa riferimento ad una tolleranza del 10%:

In corrispondenza di Vi = 100 mV si ha:

- corrente massima =  $10,496 \mu A$ ;

- corrente minima =  $9,092 \mu A$ ;

- corrente nominale =  $9,804 \mu A$ ;

L'errore di non linearità integrale è dato da:

- (corrente nominale corrente minima) =  $0.712 \mu A$  (valore massimo);

- (corrente massima corrente nominale) =  $0.692 \mu A$  (valore minimo);

Una terza simulazione fa riferimento ad una tolleranza del 5 %:

In corrispondenza di Vi = 100 mV si ha:

- corrente massima =  $10,183 \mu A$ ;

- corrente minima =  $9,43 \mu A$ ;

- corrente nominale =  $9,804 \mu A$ ;

L'errore di non linearità integrale è dato da:

- (corrente nominale corrente minima) =  $0.374 \mu A$  (valore minimo);

- (corrente massima corrente nominale) =  $0.379 \mu A$  (valore massimo);

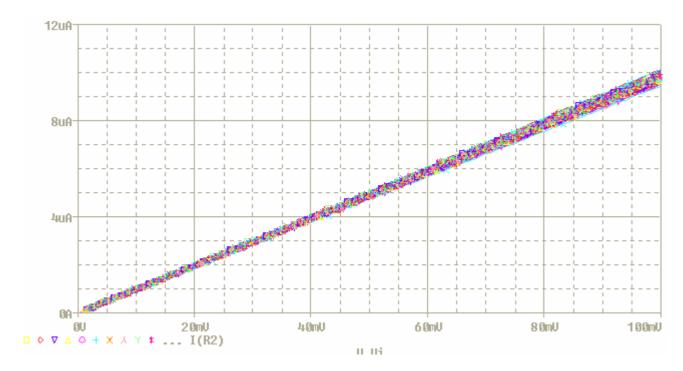

Dall'analisi di Montecarlo possiamo ottenere il seguente grafico :

Il grafico rappresenta la variazione dell'errore di non linearità integrale (preso come valore massimo) al variare della tolleranza.

### Analisi dei costi per la realizzazione del progetto

Prima di sommare tutti i costi dei singoli componenti, si ottimizza la quantità di integrati da utilizzare per la parte combinatoria del progetto:

- Sapendo che EXOR(A,B) = (A^ \* B + A \* B^), la porta può essere realizzata con 2 AND(2ingressi), 2 NOT e 1 OR(4ingressi);

- Sapendo che NAND(A,B,C,D) = (AND(AND(A,B),AND(C,D)))^, la porta può essere realizzata con 3 AND(2ingressi) e 1 NOT.

Da ciò risulta che per realizzare questa parte del progetto sono necessarie: 2 OR(4 ingressi) , 8 AND(2 ingressi) e 4 NOT(4 ingressi) .

#### Dotazione degli integrati:

- 74HC08 : 4 AND(2ingressi);

- 74HC04: 6 NOT;

- CD4030B: 4 EXOR;

- CD4072B: 2 OR (4ingressi);

- CD4013B: 2 flip-flop tipo D.

Senza nessuna ottimizzazione, considerando anche l'antirimbalzi, questa parte potrebbe essere realizzata con 6 integrati: uno per EXOR, uno per NAND, uno per OR, uno per NOT, uno per i 3 AND e uno per i due flip-flop. Per come sono dotati gli integrati si avrebbe uno spreco eccessivo di porte, mentre con l'ottimizzazione si risparmia un integrato, riducendo notevolmente lo spreco.

Per il costo dei componenti del progetto si è richiesto un preventivo alla **DS elettronica** di Casarano (LE) con l'unica variante relativa al multiplexer analogico ADG406 sostituito con il 74HC4067, avente le stesse caratteristiche e funzioni :

| componente         | quantità | prezzo     | prezzo   |

|--------------------|----------|------------|----------|

| - 477 G 40 6       |          | unitario,€ | totale,€ |

| 74HC4067           | 1        | 2,00       | 2,00     |

| 74HC191            | 1        | 0,70       | 0,70     |

| NE555              | 1        | 0,50       | 0,50     |

| 74HC08             | 2        | 1,00       | 2,00     |

| 74HC04             | 1        | 0,50       | 0,50     |

| CD4072B            | 1        | 0,50       | 0,50     |

| CD4013B            | 1        | 0,50       | 0,50     |

| Basetta in Rame    | 1        | 1,50       | 1,50     |

| Resistenza         | 15       | 0,036      | 0,54     |

| 680Ω, tol 1%       |          | 0.026      | 0.1.4.4  |

| Resistenza         | 4        | 0,036      | 0,144    |

| 1 KΩ, tol. 5%      |          | 0.026      | 0.026    |

| Resistenza         | 1        | 0,036      | 0,036    |

| 4,7 KΩ, tol 1%     |          | 0.00       | 2.2.5    |

| Resistenza         | 1        | 0,036      | 0,036    |

| 2,4 KΩ, tol 1%     |          |            |          |

| Resistenza         | 1        | 0,036      | 0,036    |

| 1,6 KΩ, tol 1%     |          |            |          |

| Condensatore       | 1        | 0,50       | 0,50     |

| 3.3nF,poliestere   |          |            |          |

| Condensatore       | 1        | 0,50       | 0,50     |

| 1nF, poliestere    |          |            |          |

| Condensatore       | 1        | 0,06       | 0,06     |

| 24μF,16V,elettrol. |          |            |          |

|                    |          | totale     | 10,05 €  |

## Conclusioni

Come dalle specifiche, il potenziometro progettato può essere destinato per applicazioni audio. Nella maggior parte dei casi gli impianti audio sono in versione stereo, ovvero ogni progetto come amplificatori, filtri, ecc. viene duplicato per due segnali indipendenti. Con qualche modifica, il potenziometro può essere realizzato in versione duale: basta aggiungere un altro stadio multiplexer - vettore resistenze – filtro passa basso e mandare lo stato del contatore in parallelo ad entrambi i multiplexer.

# **INDICE**

| Descrizione generale di un potenziometro            | pg.1    |

|-----------------------------------------------------|---------|

| Specifiche di progetto                              | pg.2    |

| Schema a blocchi del progetto                       | pg.2    |

| Descrizione schema a blocchi                        | pg.2    |

| Analisi dei singoli blocchi e loro progettazione    | pg.3    |

| Generatore di clock                                 | pg.3    |

| Breve analisi teorica del timer 555                 | pg.3    |

| Configurazione del timer per il progetto            | pg.5    |

| Contatore esadecimale                               | pg.5    |

| Breve analisi teorica sui contatori                 | pg.5    |

| Contatore utilizzato per il progetto                | pg.6    |

| Deviatore per il clock                              | pg.9    |

| Problema del clock fisso                            | pg.12   |

| Multiplexer analogico                               | pg.18   |

| Breve analisi teorica del multiplexer analogico.    | pg.18   |

| Multiplexer utilizzato per il progetto              | pg.19   |

| Vettore di resistenze.                              | pg.20   |

| Progetto del filtro per lo stadio di uscita         | pg.21   |

| Verifica di fine corsa e abilitazione Up e Down     | pg.23   |

| Antirimbalzi per i pulsanti Up e Down               | pg.26   |

| Analisi di Montecarlo                               | pg.27   |

| Analisi dei costi per la realizzazione del progetto | pg.30   |

| Conclusioni                                         | pg.32   |

|                                                     | r 0.0 = |